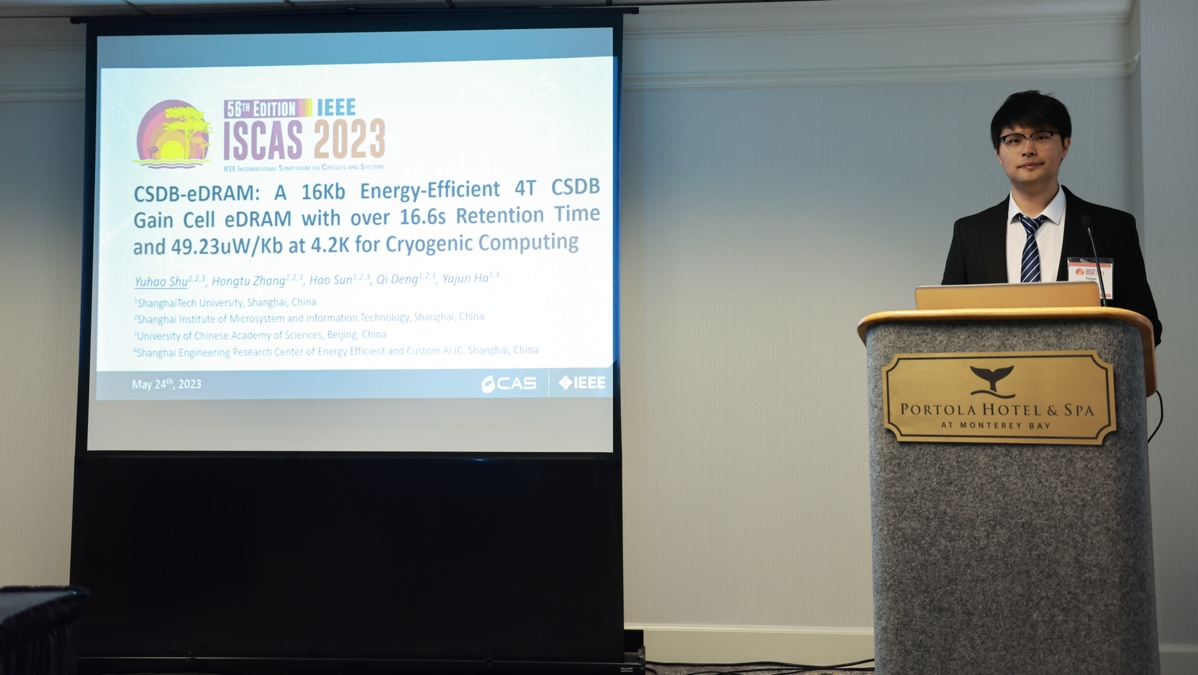

2023年IEEE International Symposium on Circuits and Systems(ISCAS)学术会议在美国加利福利亚州蒙特雷举行。该会议是电气电子工程师学会电路与系统分会(IEEE Circuits and Systems Society)旗舰会议,也是全球理论、设计和电路系统实现领域研究人员交流的首要论坛。我很荣幸与我的导师哈亚军教授一起参加本年的ISCAS活动,并报告了我所发表的文章“CSDB-eDRAM: A 16Kb Energy-Efficient 4T CSDB Gain Cell eDRAM with over 16.6s Retention Time and 49.23uW/Kb at 4.2K for Cryogenic Computing”。

低温环境能够优化器件的漏电和电阻等重要参数,进一步推动了低温计算以及相关应用的发展。存储作为计算系统的关键组成部分,往往决定了存储的数据量以及访问数据的速度。此外,低温存储器在高性能计算平台、量子计算和超导计算机等领域的应用越来越广泛。正是其在现代计算系统中的重要性以及应用广泛,存储设计成为了计算系统的关键。在各种存储拓扑中,基于增益单元的嵌入式DRAM(GC-eDRAM)由于工艺兼容性、高密度以及低功耗操作等特点,成为低温计算系统中存储实现的有力方案。

我们在本次报告中关注GC-eDRAM在提高数据保持时间、支持高性能双端口读操作和降低功耗等方面所存在的设计与挑战。并提出了一种4T CSDB 增益单元设计,无需任何增压方案,即可显著提高数据保持时间,同时支持4.2 K下的双端口读操作以提高数据带宽。我们还使用了一种基于字线电压片外调整方法以实现更高的读性能。同时,使用位线分割技术将位线的重负载分成几个本地块,以优化低温下不同访问操作的功耗开销和访问性能。

所展示的16kb低温半静态双端口无增压嵌入式DRAM低温高能效存储器(CSDB-eDRAM)已在40nm CMOS工艺中完成了流片与测试。该存储器可提供约16.67秒的数据保持时间,比国际最先进的研究工作高2.6倍,并且实现了更低的刷新功率0.11 pW/Kb。此外,它还实现了710 ps(1.41 GHz)的数据访问时间以及最低的动态功耗开销49.23 uW/Kb。该工作为低温高能效存储器的设计提供了新的思路和解决方案,可为未来的低温计算提供更好的支持。

在会议中,我和来自本研究领域的国际先进团队深入探讨了低温高能效存储与计算技术在低温量子计算等领域的应用前景以及潜在的设计挑战。通过参加此次学术会议,我对当前低温电路设计领域的发展情况有了更深入了解,并且也明确了未来的研究和发展方向。

沪公网安备 31011502006855号

沪公网安备 31011502006855号