由上科大信息学院哈亚军教授指导的研究生团队SkrSkr在最近召开的2021年集成电路设计自动化(EDA)领域顶级会议Design Automation Conference (DAC)上取得了系统设计竞赛(System Design Contest,SDC)全球第一的好成绩。这是自2019年周平强教授指导团队夺得该项竞赛季军,2020年哈亚军教授指导团队夺得亚军之后,信息学院研究生团队在该项赛事中取得的最佳战绩!

由DAC会议组织的系统设计竞赛是目前神经网络加速器设计领域最高级别的竞赛。今年共有来自全球16个国家和地区的113支队伍参与。本次比赛的任务是在Xilinx Ultra96v2平台上实现高速、高准确率且低功耗的飞行器高空目标检测深度学习算法,评价指标综合考虑速度、精度以及能耗。比赛所用的训练与测试数据集均由深圳大疆公司提供。

DAC系统设计竞赛不仅考察参赛队伍的算法能力,还考察参赛队伍硬件设计以及系统设计的能力。 参赛队伍要完成设计网络,量化网络,设计加速器,构建完整系统四个步骤的工作。其中设计网络部分需要确定采用哪些类型的算子、输入输出通道数、残差连接、级联等。设计加速器部分需要考虑计算引擎的架构、计算引擎复用策略、量化策略、并行度、乒乓操作、数据搬运以及重用等。此外设计网络,量化网络以及设计加速器这三个环节又是相互影响的,任何一个环节的小改动都会牵扯到其他两个环节,使得整个比赛的设计空间非常大。竞赛最终完成的作品是一个接近可以落地的解决方案而不只是算法,这对参赛选手提出全方位的考验。

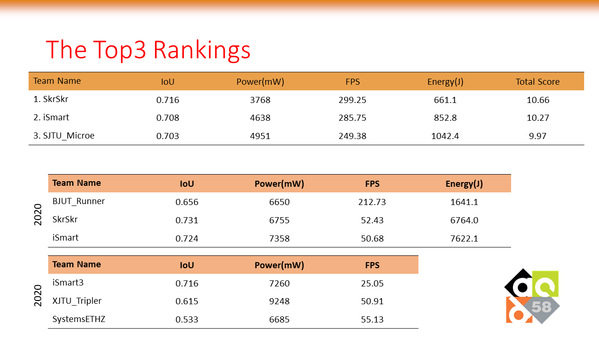

2021年比赛的评价指标与2020年类似,仅对精度的要求有所变化,从越高越好变成只要超过一定阈值(0.70)即可。因此,SkrSkr团队选择在去年获得亚军的设计基础上以精度为代价优化速度,进行多项改进。他们提出Tunable Activation Imbalance Transfer量化算法,将单加速器串行计算架构替换成了多加速器并行数据流计算架构,利用Xilinx DSP48E2的特点优化了卷积的计算引擎,此外,使用DSP自带的级联累加功能替换加法树,通过libjpegturbo库和多线程技术加速CPU读图速度。经过以上优化,除精度以外,各项指标均较2020年取得亚军的设计有显著进步。功耗下降45%,速度提升6倍,总能量降低了90%,而精度仅下降0.015。而且,团队设计作品的所有指标均优于竞争对手。

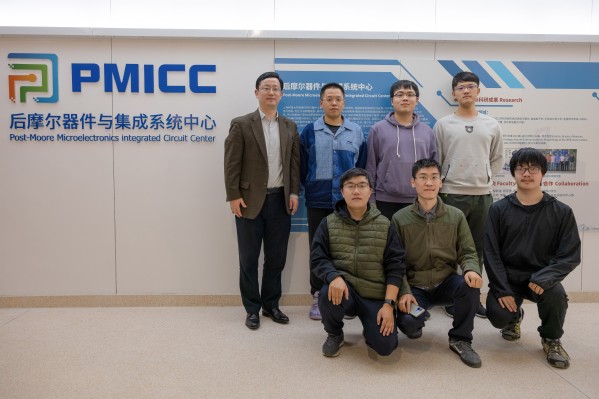

本次代表上科大参加竞赛的SkrSkr团队由信息学院7位研究生组成,他们分别是:2019级硕士研究生陈少毅、周之期,2019级博士研究生姜伟雄,张松阳,2021级博士研究生邓岂,2021级硕士研究生罗剑文,2020级博士研究生刘心哲。分别来自哈亚军、陈佰乐、何旭明教授课题组。

近年,哈亚军团队在国际高等级芯片电子设计自动化竞赛中斩获颇丰,连续在国际性学科竞赛中取得佳绩,包括:2019 ICCV-Low Power Computer Vision Contest亚军、2020 DAC-System Design Contest亚军、2020 复微杯全国大学生电子设计竞赛软件赛道冠军、2021 IEEE CEDA组织的 EDAThon马拉松冠军等。

上科大鼓励学生参加高等级国际学科竞赛,通过与国内外高校团队同场竞技,不仅锻炼了学生的知识应用能力、临场应变能力和协同合作能力,更是增进了各团队的交流合作,进一步开拓了学术视野。

沪公网安备 31011502006855号

沪公网安备 31011502006855号