我于2025年4月12日至2025年4月18日前往美国马萨诸塞州波士顿参加了由电气电子工程师学会固态电路分会(IEEE Solid-State Circuits Society)主办的定制集成电路会议(Custom Integrated Circuits Conference),出访时间为7天,会议简称为2025-CICC。该会议是专注于集成电路开发领域的顶级学术会议。会议议程融合了口头报告、展览展示、专题研讨及技术论坛等多种形式,集中呈现针对实际工程问题的原创首发技术成果与创新电路设计方法。作为业界标杆会议,CICC为参会者提供了解设计难题解决方案、提升电路设计技艺、接触前沿技术领域,以及与同行精英、论文作者及产业专家建立专业网络的绝佳平台。

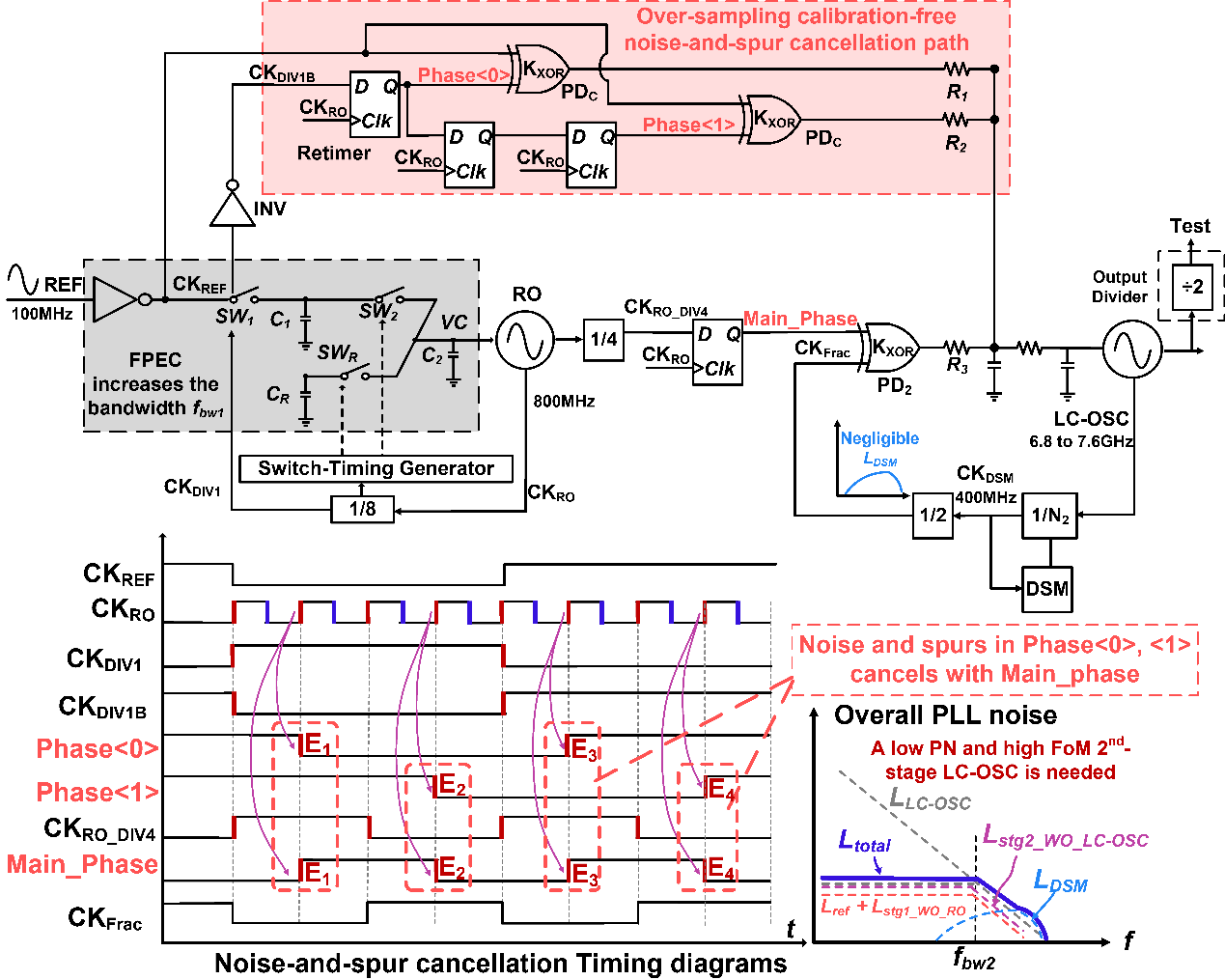

几个月前,在课题组以及导师的帮助下,我以第一作者的身份完成并投稿了学术论文 《A Fractional-N Cascaded PLL Employing the Calibration-free Noise-and-Spur Cancellation technique》。该论文致力于以免校准的方式解决小数分频锁相环(Fractional-N PLLs)量化噪声,提出了一种采用免校准噪声与杂散消除技术的小数分频级联锁相环,如图1所示。

图1 基于免校准噪声与杂散消除技术的小数分频级联锁相环架构和噪声消除时序图

该架构通过引入过采样消除路径,实现了以下目标:1)通过过采样技术实现第一级整数锁相环的全频段噪声与杂散消除,消除噪声带宽限制并避免增益校准需求;2)通过多相位路径匹配实现噪声和消除路径对工艺、电源电压以及温度变化的高鲁棒性;3)通过优化的过采样消除路径实现低于1mW的功耗开销。值得注意的是,所提出的免校准噪声与杂散消除技术具有架构可扩展性,适用于其他类型的级联锁相环实现。

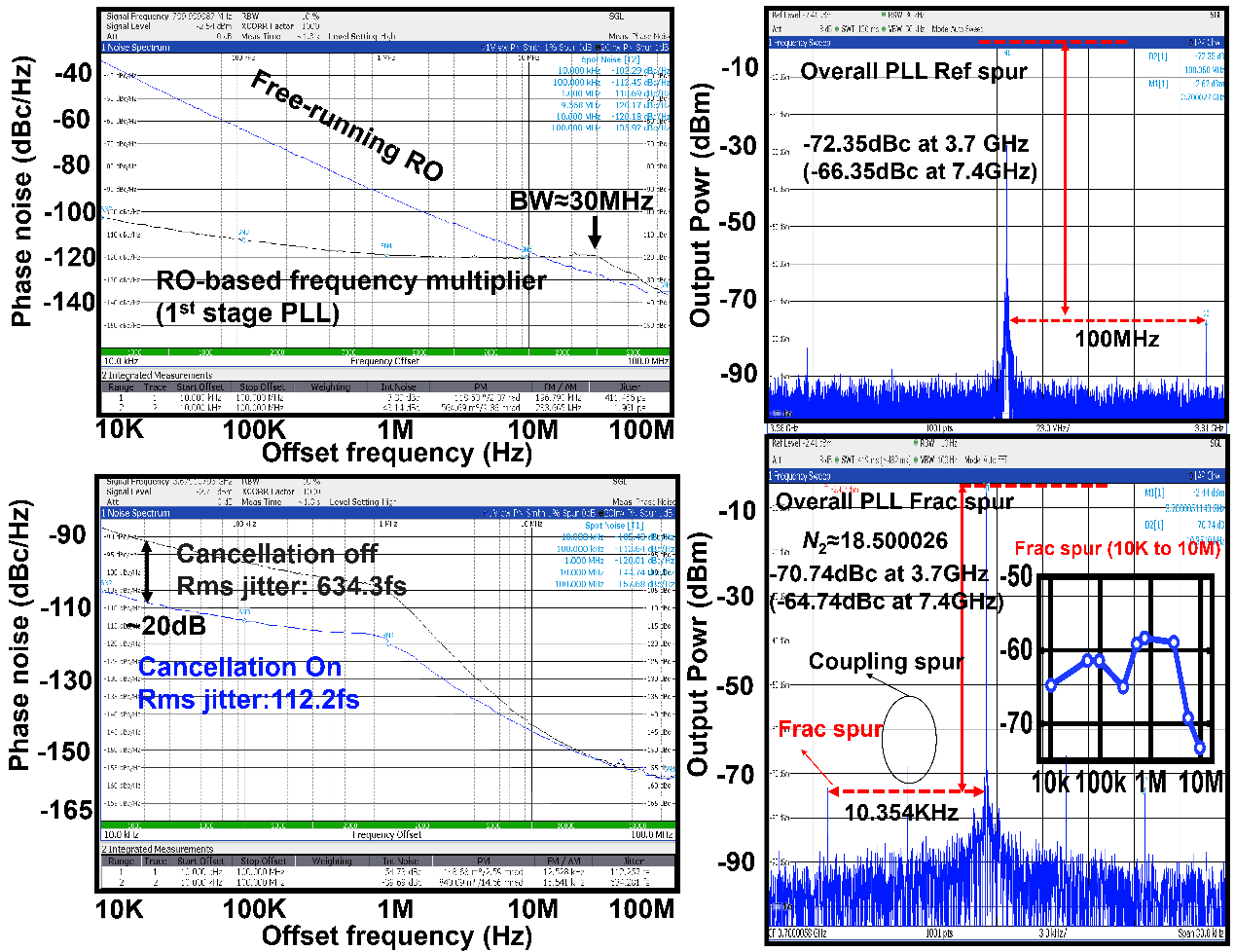

基于28 nm CMOS工艺流片的芯片实测结果表明(图2):在4.48mW功耗下实现了127.8fs均方根抖动(积分范围10kHz至100MHz),品质因数(FoM)达到-251.4dB,达到国际领先水平。所实现的消除技术将带内相位噪声和小数杂散同时降低20dB以上,在1MHz频偏处达到-113dBc/Hz的相位噪声水平,小数杂散抑制至-62dBc。本研究不仅为高频段无线通信系统提供了关键时钟解决方案,其创新架构更为未来通信系统的时钟合成技术奠定了重要基础。该论文成功被2025-CICC录用,因此我这次前往波士顿参加该会议是为了汇报我在论文中的研究成果,并于其他学者进行学术交流。

图2 第一级整数锁相环和整体级联小数锁相环项相位噪声以及杂散测试图

会议期间,我向相关领域的教授和学者汇报了论文中提出的小数锁相环架构、理论分析及芯片测试结果。在交流环节中,通过与各位研究者的深入讨论,我获得了许多建设性意见,这些反馈为我的后续研究提供了重要参考。同时,与会专家也针对我的研究提出了具体修改建议,我们还互留了联系方式,为今后的学术交流与合作奠定了基础。除汇报自身研究成果外,我还积极参与了会议的其他学术活动。通过聆听锁相环设计领域专家的专题报告,我对该技术的发展趋势有了更深入的认识。此外,我还与其他学者就各自的研究课题展开交流,进一步拓展了学术视野。

参加本次CICC会议让我受益匪浅,不仅拓宽了学术视野,也深化了对小数分频锁相环领域前沿研究的理解。在会议期间,我有幸与国际顶尖研究团队进行了深入交流,共同探讨了当前小数分频锁相环设计中的关键挑战,包括量化噪声抑制、宽带杂散优化、低功耗架构设计等核心问题。通过聆听多位专家的报告及参与技术讨论,我对该领域的最新进展,如数字小数锁相环技术、超低抖动时钟合成方案等创新方法有了更系统的认识。

此外,此次会议让我更清晰地把握了未来研究方向,尤其是在面向5G/6G通信、高速数据转换器等应用场景下,如何进一步提升小数分频锁相环的性能极限。与行业领先学者的互动不仅启发了我的研究思路,也为后续的科研合作奠定了良好基础。总体而言,本次会议不仅强化了我的专业知识,也帮助我更好地定位自身研究在学术和产业界的价值,对未来的科研工作具有重要的指导意义。

沪公网安备 31011502006855号

沪公网安备 31011502006855号