7月24日,由上海科技大学信息学院组织的“楷登电子(Cadence)集成电路暑期实训”圆满结束。本次实训6月30日开营,为期25天,是上科大电子学科平台与楷登电子开展的第二期暑期实训。本次实训在去年的基础上,设立了基础班和提高班,以满足不同背景学生的需求。

纳米工艺大规模集成电路(VLSI)

物理设计

基础工具班

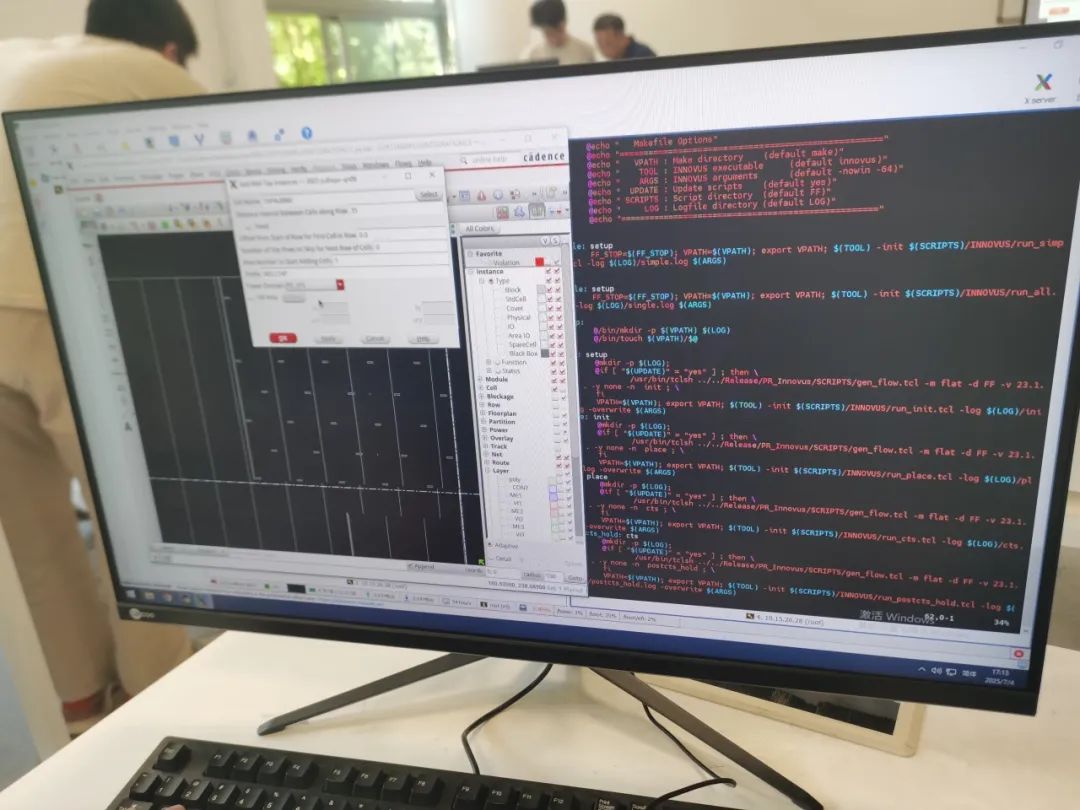

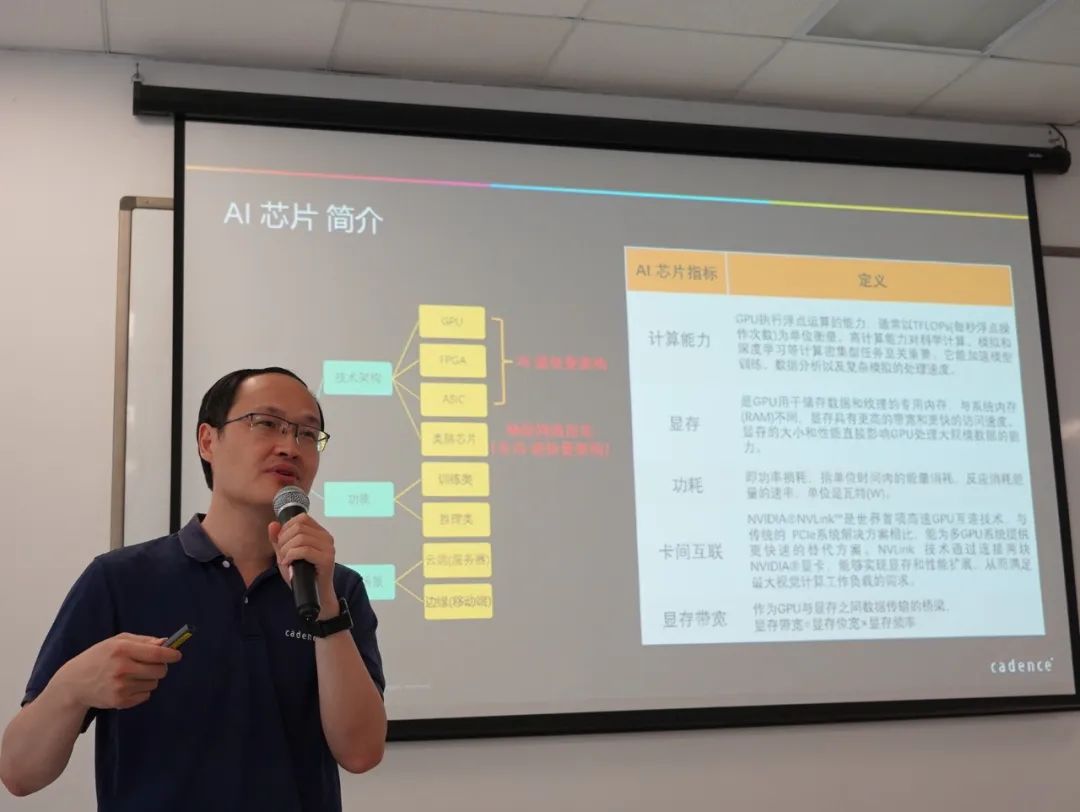

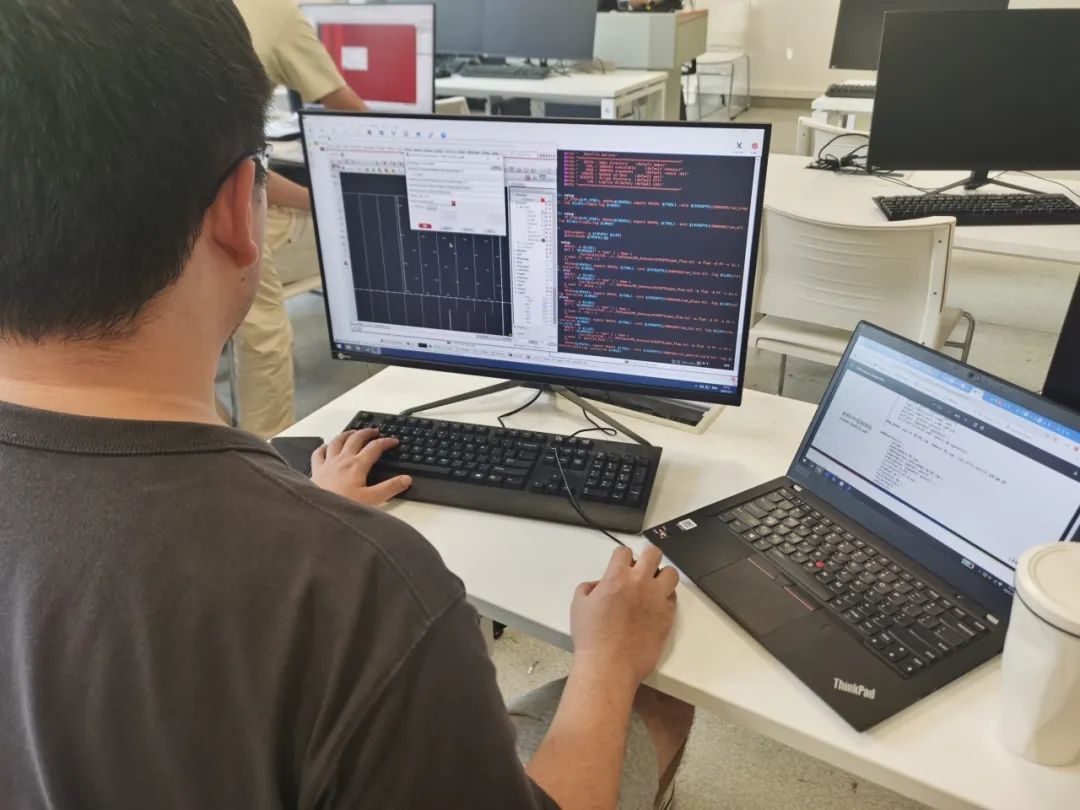

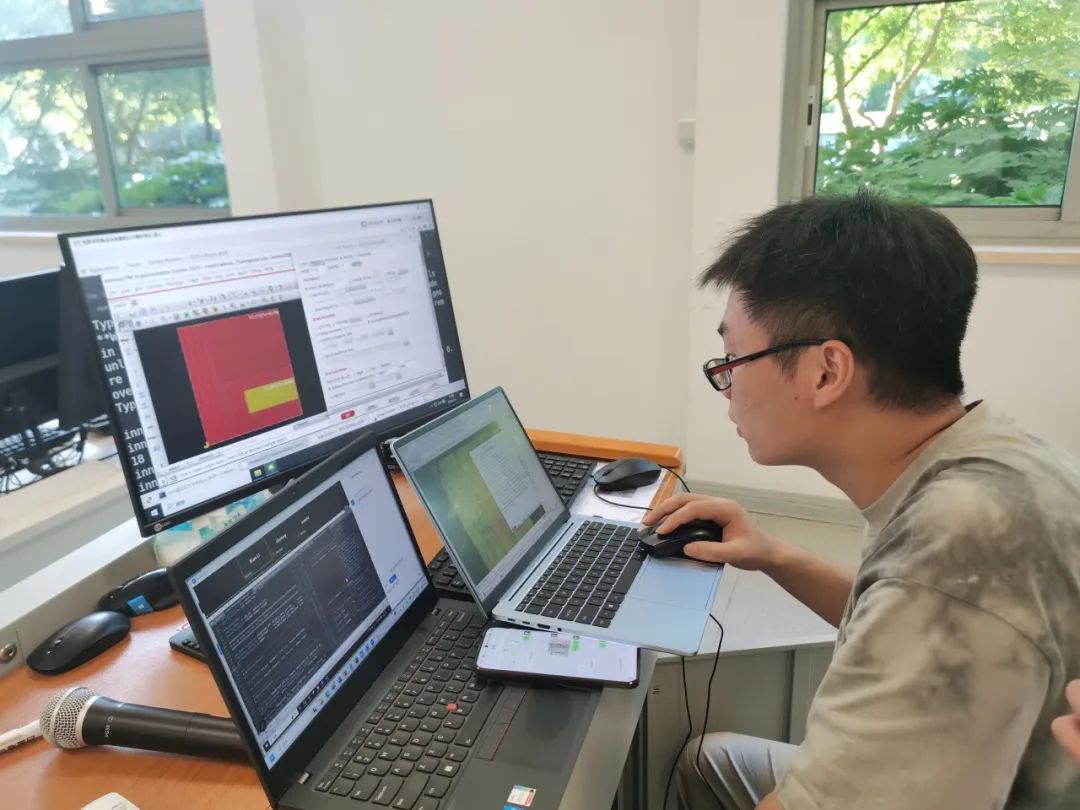

信息学院电子学科平台协调楷登电子的20余位行业资深技术专家及助教开展教学。基础班聚焦“纳米工艺大规模集成电路(VLSI)物理设计与实现”,从数字芯片设计的综合工具Genus出发,介绍了从RTL到门级网表的实现;介绍了业界主流后端设计工具Innovus,并详细讲授在Innovus中如何对芯片做布局,包括Floorplan的设计,电源的布局和优化,模块设计的物理布局等等;专题介绍了芯片设计中的时钟树设计和优化;介绍了先进工艺节点下如何利用工具来布线和优化;在签核课程中,结合实际案例,介绍如何利用Tempus来做时序检查,违例分析排查等。

理论学习结合丰富的实践操作环节,使学生们切实学到了业界先进的EDA设计工具及流程,了解了前沿技术动态,有助于其未来职业规划发展的思考,强化了学生的卓越工程能力和技术创新能力,为上海科技大学信息学院集成电路领域的创新型、复合型、应用型人才培养加油助力,为电子设计行业的发展增砖添瓦。

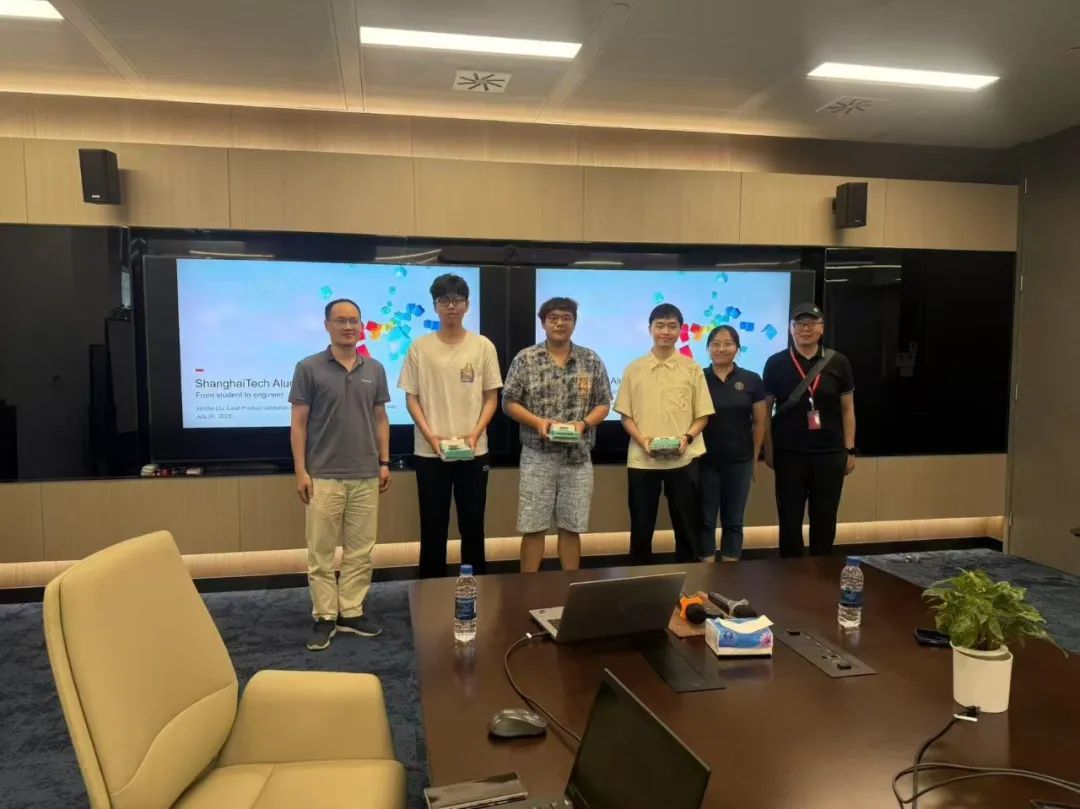

本次基础工具班共有65名同学参加,其中61名同学获得了结业证书,10名同学获得了优秀营员证书。信息学院副院长周平强教授代表学院感谢楷登电子的支持,并向其颁发了感谢证书。他鼓励学员们珍惜机会,厚积薄发,努力使自己成为集成电路行业的栋梁之才。楷登电子数字与签核研发事业部产品资深高级总监刘淼先生也为学员送上学习建议和祝福,鼓励大家积硅步,方能致千里。

(右划查看更多)

楷登电子作为连续十年名列美国《财富》杂志评选的“100家最适合工作的公司”之一,在基础班的结营仪式上,其中国区人事部门代表也在现场介绍了公司概况和招聘渠道,为学员的职业规划提供指导。楷登电子大学合作项目总监Tracy女士不仅为学员们带来了纪念品,还与学院老师协作,在培训结束后为学员开通楷登在线支持平台账号,以支持其后续学习。

滑动查看更多

纳米工艺大规模集成电路(VLSI)

物理设计

提高班

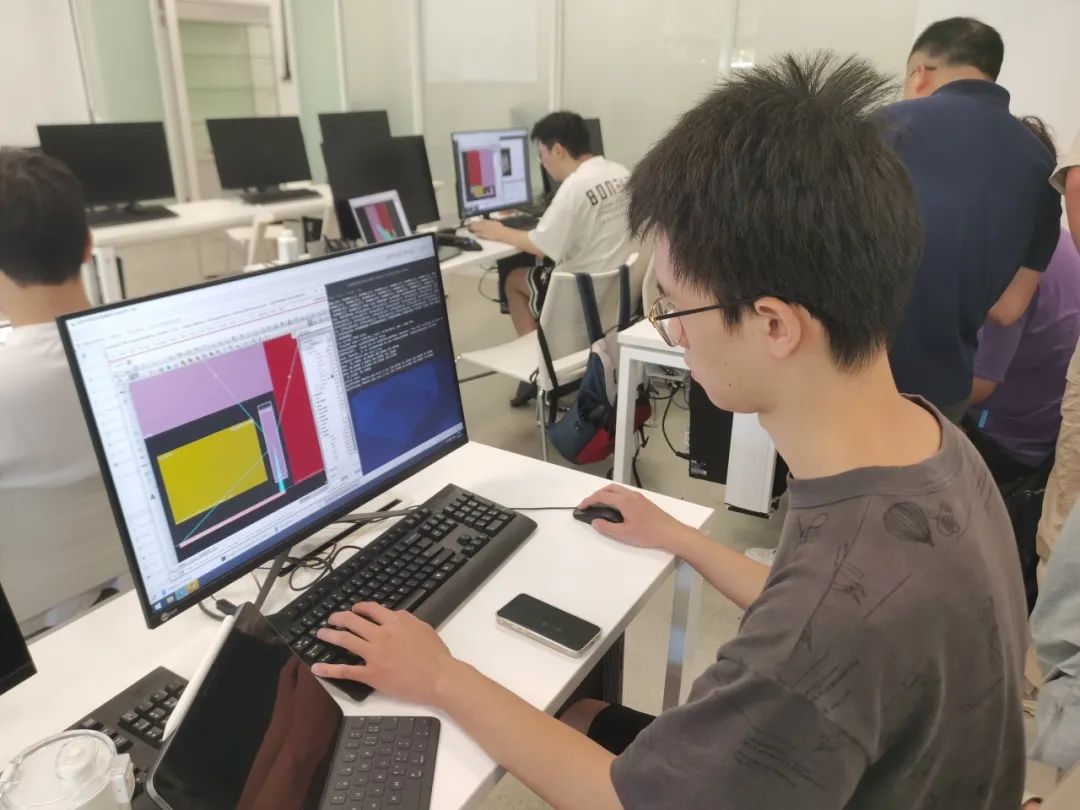

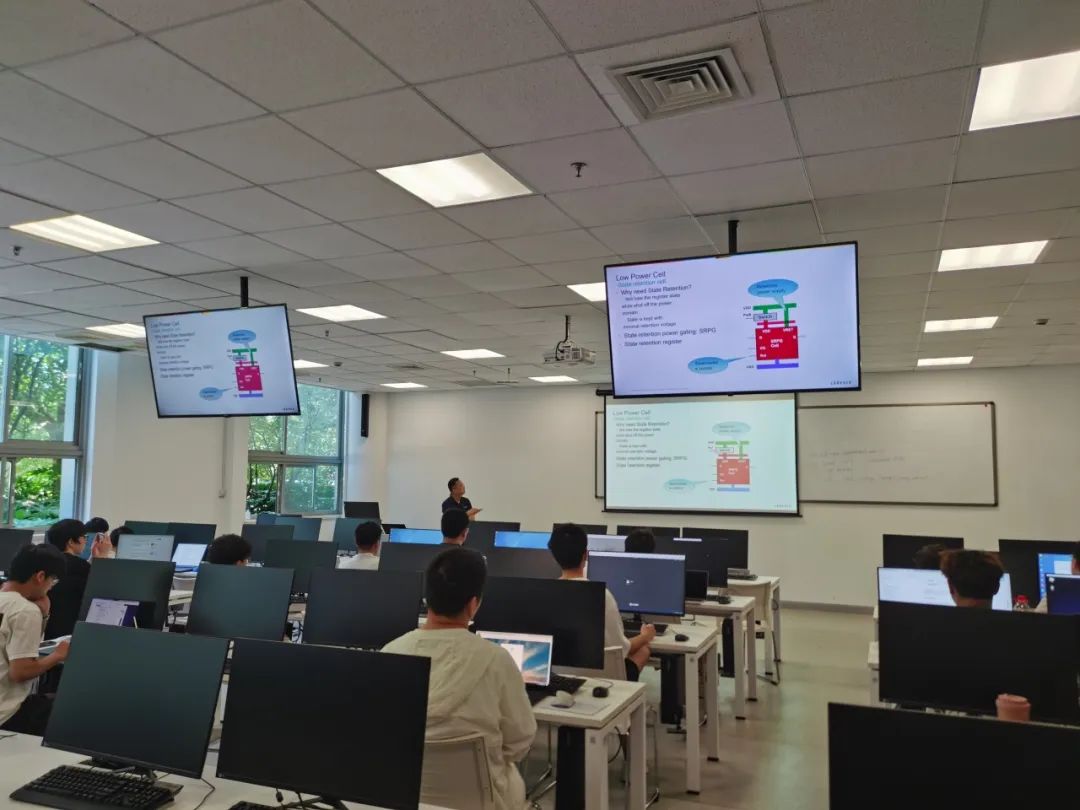

在掌握了基础工具的使用方法后,23名学员参与了低功耗数字全流程的培训。培训以实操为主,楷登电子的技术专家首先讲解基于ARM Cortex-M0核的低功耗实现流程,随后学员需自主完成基于ARM Cortex-M7核的低功耗实现项目。过程中采取“学员发现问题、专家共同讨论、协作解决问题”的模式,强化了学员的独立思考和互动能力,加深了对项目关键点的理解。

(右划查看更多)

根据学习表现及项目完成度,共有6名同学获得了提高班的获奖证书及奖品。7月24日结营当天,全体提高班学员在带队老师指导下参观了楷登电子上海前滩研发中心,与研发人员和优秀校友面对面进行了交流讨论。

(右划查看更多)

本次活动的顺利开展,得到了楷登电子、上科大信息学院电子学科平台及图信中心的大力支持。

学员说

我是去年就参加过Cadence暑期实训基础班的同学,来自企业的专家们指导我熟悉了许多常用软件的操作,使我感到受益匪浅。今年有幸参加了Cadence举办的低功耗设计进阶培训,几位技术专家由浅入深地讲授了设计的流程和要点,手把手地带领同学们迭代并优化自己的设计方案。我在“自我驱动思考+专家辅助指导”的模式下学到了很多东西,深化了对数字电路设计流程的理解。不夸张地说,我认为这是我参加过最有价值的培训,感谢学校的老师和教授们,以及来自企业的专家们能提供给我如此宝贵的学习机会。我还想特别感谢提高班的主讲专家(大家亲切地称呼他为彪哥:D),他的耐心指导使我获益良多!

----2023级硕士研究生奚琛博

这次实训给了我一次非常好的机会,让我通过实践学习完成了低功耗设计流程。在基于ARM Cortex-M7的小型项目中,Cadence的老师提供了关键、细致的指导,及时解答了我在工具使用和设计思路上的疑问;同时,项目本身留有很大的探索空间,可以根据需要查阅软件手册尝试不同的优化命令,从中学到了很多工具的使用技巧,也更深入地理解了低功耗设计的实现细节。整个过程不仅让我积累了宝贵的实操经验,也为今后更好地衔接前后端设计打下了基础。

----2023级硕士研究生周俊晟

感谢 Cadence 和信息学院提供的宝贵培训机会,让我得以深入了解低功耗设计的原理与实现细节。基于 ARM-M7 内核,我学习并实践了使用 Innovus 等工具进行低功耗数字后端设计,包括多电源域的 floorplan 规划、电源网络构建、时钟树综合与布线优化等关键流程。在项目中,我深入探索了如何结合架构特点优化布局、合理划分电源域以提升能效,并通过时钟树优化改善整体时序性能。在 Cadence 专家的指导下,我对低功耗设计有了更系统和深入的理解。本次培训不仅拓宽了我在数字 IC 设计领域的技术视野,也为我未来在集成电路设计方向的深入研究与职业发展奠定了坚实基础。

----2025级博士研究生王宇同

今年夏天,我有幸参加了由 Cadence 与学院联合举办的 “Digital and Signoff Full Flow Tools Training” 夏令营。作为一名主要从事自旋电子研究的学生,这次培训对我来说是一段非常宝贵的跨领域学习经历。课程内容主要围绕数字 IC 设计的后端流程展开,我学习了 Genius、Tempus 和 Innovus 等工具,对数字芯片设计的整体流程有了初步的认识。虽然我的专业背景和数字后端设计关系不大,但在培训过程中仍收获颇丰,不仅拓宽了视野,也增进了我对 EDA 工具和数字设计流程的理解。Cadence 的工程师老师们讲解非常细致,对我提出的一些略显突兀的“外行”问题也都耐心解答,让我非常感动,也更加珍惜这次难得的学习机会。

----2023级博士研究生张雪

在此次参加Cadence低功耗设计培训中,我受益匪浅。培训内容涵盖了我平时很少接触的多电压域设计,使我对低功耗设计有了更深入的理解。我学习了多种低功耗设计方法,包括低功耗单元的使用、低功耗floorplan的构建,以及工具中实现功耗优化的相关指令等,极大地拓展了我的专业知识面。通过本次学习,我不仅提升了实践能力,还荣幸地获得了奖项和Cadence提供的奖品,倍感鼓舞。衷心感谢学校与Cadence给予的宝贵学习机会,我将继续努力,不断进步,争取在未来取得更加优异的成绩。

----2023级博士研究生刘昊天

时间匆匆而过,学院和Cadence组织的提高班转眼就到了尾声。在这接近一个月的学习时间里,我学到了很多关于后端方面低功耗设计的技能,例如power domain的合理规划,电源网络的配置,如何添加power switch,以及其他对功耗的优化方法。对于第一次接触低功耗设计,难免遇到诸多问题,但是Cadence的几位培训老师都一一为我解答,而且还会在我提出的问题上进行拓展补充并分享他们的经验。很幸运能够参加提高班,也很感谢学院提供的机会和Cadence的各位老师的教导。

----2023级博士研究生王善来

沪公网安备 31011502006855号

沪公网安备 31011502006855号