近日,上海科技大学信息科学与技术学院后摩尔与集成系统中心多篇成果被2024年ACM/IEEE设计自动化国际会议(ACM/IEEE Design and Automation Conference,DAC)接收录用。DAC有超过60年的举办历史,是(芯片)电子设计自动化领域的重要学术会议,在半导体与集成电路设计领域有着深远影响。本届DAC将在美国旧金山召开。

基于空间稀疏性的神经网络体渲染算法的专用硬件加速器(ZeroTetris: A Spacial Feature Similarity-based Sparse MLP Engine for Neural Volume Rendering )

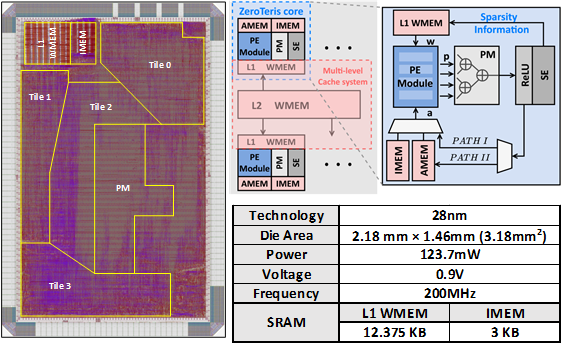

神经网络体渲染(Neural Volume Rendering, NVR)是用于生成多视角高质量图片的新范式,近年来发展迅速。但NVR所需的大量计算使其难以直接部署到现有的神经网络加速器上。研究团队设计了一种利用多层感知器矩阵中具有空间相似的稀疏性质来加速NVR算法的硬件——ZeroTetris。通过利用NVR算法中相邻采样点之间的稀疏性,ZeroTetris能够有效地跳过激活层中与0相关的计算,从而提高计算效率并降低能耗。研究人员还对ZeroTetris进行了28nm工艺的逻辑综合、布局和布线等后端流程。仿真实验结果证明,与其他硬件加速器设计相比,ZeroTetris在面积利用率和能效方面表现卓越。

图1 ZeroTeris加速器设计

上海科技大学信息学院2023级博士生万浩川为论文第一作者,信息学院虞晶怡教授和娄鑫教授为共同通讯作者。研究合作者还包括信息学院2020级本科生马霖杰、2023级博士生李安童、周平强教授。

基于设计规格感知与贝叶斯优化的SoC设计空间探索框架(Knowing The Spec to Explore The Design via Transformed Bayesian Optimization)

人工智能技术的蓬勃发展使得对硬件算力的需求爆炸式增长。片上系统(System-on-Chip,SoC)的设计空间探索(Design Space Exploration, DSE)旨在快速探索综合性能指标优异的SoC微架构,从而加快设计周期,降低芯片设计成本。本研究提出了一种基于贝叶斯优化的SoC设计空间探索框架:通过设计专用的高斯过程回归模型与采集函数,并结合设计规格(Design Spec)中的信息加速探索符合设计规格要求的微架构:基于开源RISC-V SoC与神经网络加速器平台Gemmini, 使用开源7纳米工艺库进行综合与仿真,部署多种大语言模型以获得微架构的各项评估指标。与其他方法相比,该框架可以更高效地探索设计空间,也更符合现实的芯片设计场景。

图2 设计空间探索算法流程与部分实验结果

信息学院2022级硕士研究生骆东迩与浙江大学研究员孙奇为共同第一作者,耿浩教授为通讯作者,上海科技大学为第一完成单位。合作者还包括信息学院2023级硕士研究生李炘恒、香港中文大学博士研究生白晨与余备教授。

一种基于模拟分叉算法的高性能随机计算伊辛机实现(A High-Performance Stochastic Simulated Bifurcation Ising Machine)

组合优化问题是最优化问题中的一类,用于找到一组离散变量组合中的最优解,在诸多行业都有广泛的应用,可用于解决任务调度、路线规划、芯片布局等问题。伊辛机(Ising machines)在解决组合优化问题时具有较高性能(polynomial time),近期受到更多关注。相较基于物理模型的伊辛机实现(如量子计算机等),基于模拟计算模型的伊辛机具有计算精度更高、可求解问题规模更大等优势。但其对计算资源需求较高。为了保持其求解性能并降低硬件开销,研究人员设计了定制化的高性能随机计算伊辛机求解系统,并在一个最大割问题上进行了验证。实验结果表明,所设计的随机计算伊辛机在得到接近最优解的情况下,可兼顾计算性能与硬件开销。相比目前已有的伊辛机实现,本研究设计支持稠密问题求解,潜在应用范围更广,且硬件开销更小。

图3 基于模拟分叉算法的随机计算伊辛机架构模型

信息学院2021级硕士研究生张泓桥、2023级硕士研究生余正坤分列第二、第三作者,承担了设计的软硬件仿真,刘思廷教授为通讯作者。合作者还包括加拿大阿尔伯塔大学博士研究生张婷婷与韩杰教授。

沪公网安备 31011502006855号

沪公网安备 31011502006855号