近日,我院哈亚军课题组的大四本科生李睿以第一作者身份向国际会议ACM/IEEE Design Automation Conference (DAC 2020) 投稿的论文被接收(论文题目:DVFS-Based Scrubbing Scheduling for Reliability Maximization on Parallel Tasks in SRAM-based FPGAs)。这是李睿同学今年在国际会议上被接收的第二篇科研论文。早前他以第二作者身份参与的论文被IEEE电路与系统方向的旗舰会议International Symposium on Circuits and Systems (ISCAS 2020)接收。

基于静态RAM(SRAM)的现场可编程门阵列(FPGA)是卫星及智能车等应用领域的优选高能效计算平台。它具有强大的计算能力和超高性能,并具有可重新配置电路的灵活性。同时相对于专用芯片ASIC,FPGA具有低成本和上市快的显著优点。但是基于SRAM的FPGA最初并不是为了高可靠性场景而设计研发,就可靠性而言,存储在SRAM中的数据在高辐射环境下容易被外界影响,从而引发数据翻转变得不稳定。为了解决这个问题,哈亚军课题组提出了新型的基于动态电压频率调整(DVFS)的FPGA刷新机制,并开发出一套优化算法使SRAM在被调用前能最大化提高被刷新的机会。相较于业界现在采用的三重模块冗余方法,刷新机制利用了FPGA的可编程性,从而避免了大量硬件冗余。相比其他最新相关研究,这项工作能提高36.1%的系统稳定性,基本无硬件额外开销,使得基于SRAM的FPGA可以运用于航天和智能汽车等对电路稳定要求较高的领域。

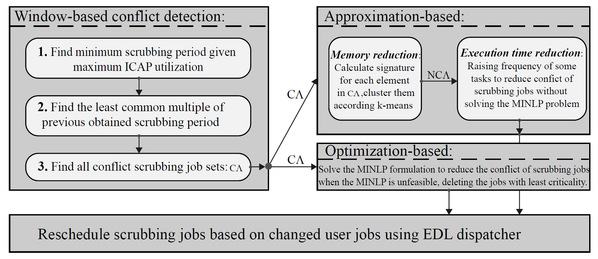

文章提出的方法

ACM/IEEE DAC会议是集成电路辅助设计(EDA)和嵌入式系统领域的国际最权威会议, 迄今已有超过50年的历史,主要关注芯片、电路以及系统设计的新工具和新方法。该会议近两年的论文接收率为20%左右。每年大陆学者在DAC会议上发表论文数量不多,而以本科生作为第一作者发表的论文更是罕见。今年的DAC学术会议将于7月19日至23日于美国旧金山举办,届时将会吸引众多科学家、研究者和工业界人士同台交流,为未来的研究提供更多思路和启发。

ACM/IEEE DAC 大会海报

今年哈亚军课题组有多篇文章被国际顶级会议和期刊接收,这几篇文章均以上海科技大学为第一完成单位。哈亚军教授回国后创立了可重构与智能硬件实验室并担任后摩尔器件与集成系统研究中心主任,现已形成包括博士生、硕士生、本科生在内近15人的科研团队。几年来,该团队专注于FPGA结构和设计工具,超低功耗数字电路与系统设计,应用于智能汽车及机器人的定制计算系统设计等的研究,并将诸多成果发表在了国际顶级期刊和会议上。实验室十分重视学生培养,尤其重视包括本科生在内所有组员的批判性思维和创新思维能力的提升。李睿同学今年夏天将在哈亚军课题组开始研究生阶段的学习。

李睿同学

沪公网安备 31011502006855号

沪公网安备 31011502006855号