2023年IEEE Custom Integrated Circuits Conference(CICC)学术会议在美国德克萨斯州圣安东尼奥举行。该会议由电气电子工程师学会固态电路分会(IEEE Solid-State Circuits Society)主办,是国际集成电路领域的旗舰会议之一。我很荣幸与导师哈亚军教授一起参加本年的CICC活动,并报告了我所发表的文章“CIMC: A 603TOPS/W In-Memory-Computing C3T Macro with Boolean/Convolutional Operation for Cryogenic Computing”。同时,我还代表课题组李怡霏师妹报告了她的研究工作“A 40nm 0.35V 25MHz Half-Select Disturb-Free Bit-interleaving 10T SRAM With Data-Aware Write-Path”。

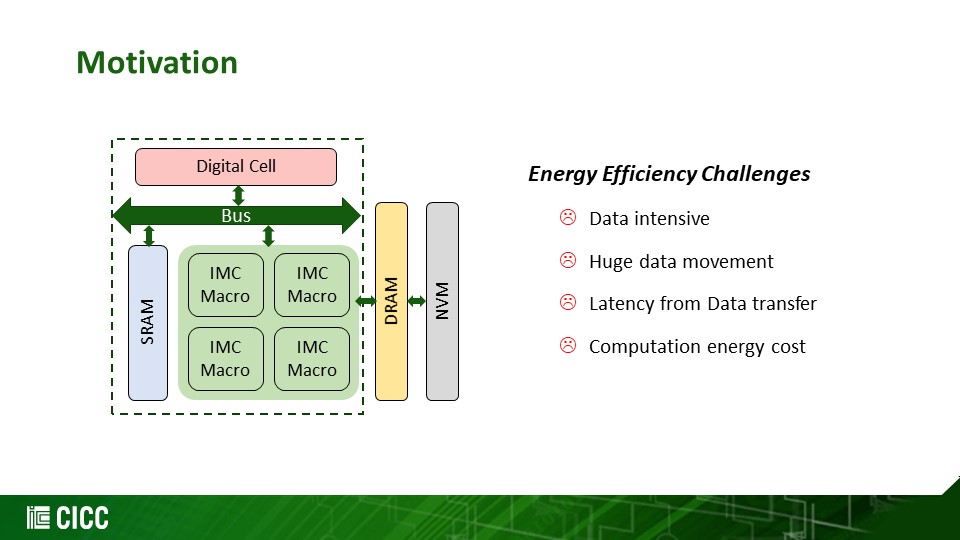

本次报告的主题是低温高能效存内计算加速器(CIMC)的设计。存内计算是解决传统冯诺依曼计算架构中存储墙问题的一种有效技术。在需要大量数据移动、数据传输延迟显著,且计算能耗较高的场景下,通过消除内存和计算单元之间频繁的数据移动,此技术可以实现更高计算能效。另一方面,低温计算旨在通过在极低温度下运行电路来提高电路的能效。虽然在低温下,晶体管的阈值电压会增加,但晶体管载流子迁移率、亚阈值摆幅和线路电阻等其他因素会得到改善,从而提高整个电路的性能。这种技术有望应用于卫星、探测器和数据中心等能源高效计算应用。通过结合存内计算和低温计算,可以进一步提升计算能效,为未来更可持续的计算提供有力的解决思路。

虽然存内计算具有极大的能效提升潜力,但在低温下操作时仍然存在一些需要解决的挑战。其中一个主要挑战是可靠的比特单元设计。在低温下,比特单元的稳定性可能会受到影响,这可能会导致内存操作出现错误。因此,开发可在低温下高效运作的可靠比特单元设计非常重要。另一个挑战是支持多种操作模式。除了基本的数据访问操作外,在不增加硬件资源开销的情况下同时支持布尔和卷积操作将进一步拓展计算应用场景。因此,开发能够支持多种操作的存内计算宏模块设计是非常重要的。最后,还有模拟数字转换器(ADC)设计开销的挑战。ADC常用作模拟域存内计算架构,并实现将模拟卷积计算结果转换为数字信号,影响到最终的计算精度以及计算能效。但是,常见的ADC的设计较为复杂并将增加整个系统硬件资源开销。因此,需要为存内计算开发快速且高能效的ADC电路。

在本次会议中,我报告了关于低温高能效存内计算加速器(CIMC)设计的成果。我们的CIMC采用了可靠的低温3T(C3T)增益单元设计,保证了数据的全摆幅传输,无需任何辅助电路,并支持可靠的计算操作。此外,我们还利用自适应参考电平放大器(ARSAs)实现了低温布尔函数,通过自适应采样方案获得布尔和卷积计算的参考电压。最后,我们基于设计的ARSA并结合其可重构性的特点实现了快速低功耗的Flash ADC。CIMC实现了平均能效603 TOPS/W,比国际最先进的研究工作高2.37倍。此外,我们的设计也保持着较高的平均计算密度284 TOPS/mm2。

在本次会议中,我和本研究领域的国际先进团队深入探讨了存内计算技术在人工智能、图像处理、自然语言处理等领域的应用前景以及潜在的设计挑战。通过参加此次学术会议,我对当前存内计算领域的发展情况有了更深入了解,也进一步明确了未来的研究和发展方向。

沪公网安备 31011502006855号

沪公网安备 31011502006855号