2024年10月,我应邀前往美国纽瓦克,参加ICCAD会议,同时作了题为”Is Vanilla Bayesian Optimization Enough for High-Dimensional Architecture Design Optimization?”的学术汇报。

我于10月26日上午从上海出发,经13小时的飞机,于当地时间 10月26日下午抵达美国纽瓦克。我的合作文章题为”Is Vanilla Bayesian Optimization Enough for High-Dimensional Architecture Design Optimization?”。该研究使用了蒙特卡洛树来应对设计空间探索中的高维问题。随着人工智能(特别是大语言模型)飞速发展,对专门优化的AI加速芯片需求越来越迫切,然而芯片设计过程中参数众多且性能指标互相矛盾,传统的人工调优方式已经难以满足快速发展的需求,因此催生了自动化的芯片设计空间探索方法(DSE)。DSE通过自动搜索和优化设计参数空间,从而找到性能(周期、功耗、面积)最优的芯片架构配置。然而,当参数维度较高时,设计空间呈指数级增长,传统的贝叶斯优化和机器学习方法难以高效处理,因此研究者不断探索更高效、更可解释的方法来解决高维DSE问题。这篇文章提出的MCT-Explorer即是这一领域最新的研究成果之一,探讨了如何高效地进行高维设计空间探索(Design Space Exploration, DSE)。面对人工智能尤其是大语言模型(LLM)对系统级芯片(SoC)设计提出的严苛性能要求,传统手动设计方法耗时且成本极高,因此需要高效自动化的方法来优化设计参数。

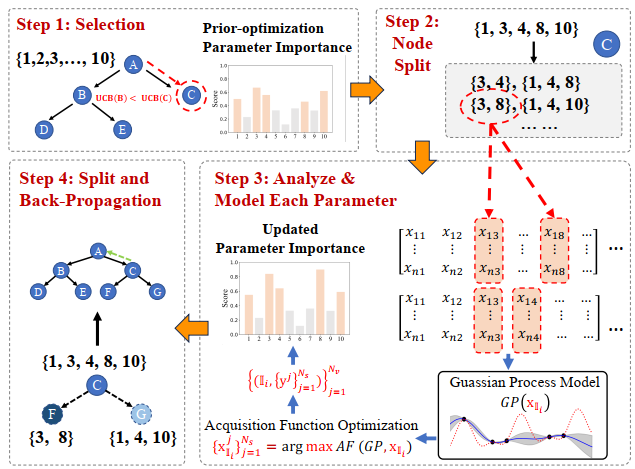

我们的工作指出,传统的贝叶斯优化方法在处理复杂SoC设计参数时,存在维度灾难(参数数量高达数十甚至数百个),导致搜索空间巨大(超过10^30),严重影响优化效率和模型精度。为了解决这些问题,我们提出了一种名MCT-Explorer的框架,核心创新包括:1、基于蒙特卡洛树搜索(Monte Carlo Tree Search, MCTS)的参数重要性分析:使用MCTS动态分析并选择对设计性能影响最大的关键参数,从而引导搜索方向,有效降低了模型拟合难度并提高探索效率。2、多目标优化策略:提出了信息引导(information-guided)的多目标贝叶斯优化方法,优化芯片设计的多个性能指标(如周期数、面积、功耗),使得优化更加平衡且有效。3、可解释性提升:MCT-Explorer不仅提升了优化效率,还为参数优化提供了明确的指导和深入的见解,增强了方法的可解释性。实验结果表明,该框架在高维(最高达270个参数)复杂的LLM SoC设计任务中显著超越传统方法,能在更短的时间内获得更优的性能表现。

这次ICCAD 2024之行,不仅让我在学术上有所收获,也让我体验了不同的文化与生活方式。正如贝叶斯优化在高维空间中寻找最优解一样,我们的人生旅途也需要在各种选择中找到平衡。希望未来有更多这样的机会,让我在学术与生活的探索中不断前行。